## Parlez-vous CAN ?

CAN et CNA sont des circuits qui assurent la fonction d'interface entre un système entièrement numérique (calculateur) et les systèmes analogiques (capteurs, actionneurs, ...)

Un CNA assure la transposition d'une valeur représentée numériquement en une grandeur tension ou courant proportionnelle à cette valeur numérique. Le coefficient de proportionnalité est appelé pas de conversion ou pas de progression.

Un CAN n bits fait correspondre à une tension continue constante appelée échantillon, un code de sortie numérique sur n bits. La fonction de conversion est définie par le nombre de pas de quantification inscrits dans l'amplitude de l'échantillon. Les notes d'application décrivent souvent si des non linéarités de loi de conversion existent.

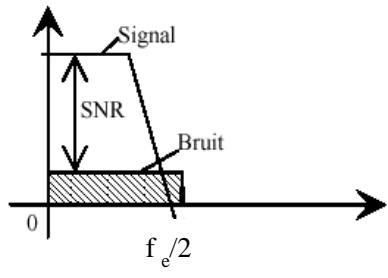

Le choix d'un CAN peut aussi découler du cahier des charges fixant le SNR.

La définition de  $f_{\max}$ , bande spectrale effective du système à numériser, est très importante puisqu'elle conditionne le choix de  $f_e$ , fréquence d'échantillonnage du CAN, avec la condition minimale du théorème de Shannon :  $f_e > 2 f_{\max}$ . On veillera à vérifier la présence du filtre anti repliement (anti aliasing filter) qui borne le signal à numériser à  $f_{\max}$ .

Trois paramètres définissent les caractéristiques d'un CAN : la pleine échelle (Full Scale Range) donnée par les tensions minimale et maximale autorisées pour l'échantillon, le nombre de bits qui assure la précision sur le codage de l'amplitude et la fréquence d'échantillonnage qui délimite la précision du spectre pouvant être reconstitué.

Vitesse de conversion et nombre de bits élevés induisent un débit d'information conséquent et la nécessité de stocker les données. Des techniques de compression de données permettent de réduire le débit d'information.

L'utilisateur devra toujours vérifier si le niveau de bruit de son système analogique est compatible avec la précision du CAN pour éviter de traiter des bits non significatifs noyés dans le bruit.

On peut (on doit) ne pas hésiter à prélever les échantillons plus vites que la variation du process observé et ne stocker que la moyenne pour améliorer la précision de conversion

## I. CAN

### a) Loi de codage

Si on considère une tension analogique  $u_b$  à l'instant b, il ne faut pas confondre la représentation binaire  $(u_b)_2$  du nombre et le codage issu d'un CAN n bits défini par les relations :

- dans le cas d'un codage par troncature (ou valeur inférieure) :

- si  $u_b \in [p\Delta, (p+1)\Delta[$  alors le CAN codera en sortie sur les n bits la valeur  $(p)_2$ .

- dans le cas d'un codage par arrondi :

- si  $u_b \in [(p - \frac{1}{2})\Delta, (p + \frac{1}{2})\Delta[$  alors le CAN codera en sortie  $(p)_2$

avec :

$$\Delta = \frac{PE}{2^n}, \text{ pas de quantification où } n : \text{Nombre de bits du convertisseur et PE :}$$

*Pleine Echelle* du convertisseur ( en anglais Full Scale Range )

### b) Nombre de bits et rapport signal sur bruit.

...on démontre ainsi que le rapport signal sur bruit exprimé en décibel prend la forme linéaire :

$$\left( \frac{U_{RMS}}{e_{RMS}} \right) = 6,02n - 4,26 \text{ pour un codage par troncature avec le type de signal d'entrée défini}$$

$$\frac{U_{RMS}}{e_{RMS}} = 6,02n + 1,76 \text{ pour un codage par arrondi avec le type de signal d'entrée défini}$$

4AE SE « Chaines d'acquisition »

auteur : JY. FOURNIOLS

CAN et concepts

## Pannel de solutions et architectures et type de sorties

| Résolution | Nombre de canaux    | Type d'interface                     | Taux d'échantillonage             | Type d'entrée                                 |

|------------|---------------------|--------------------------------------|-----------------------------------|-----------------------------------------------|

| 6 bit      | 1 Channel           | 1-Wire, I2C                          | 3.75 S/s                          | Differential                                  |

| 7 bit      | 1 Channel/2 Channel | 3-Wire                               | 3.75 S/s, 15 S/s, 60 S/s, 240 S/s | Differential/Pseudo-Differential              |

| 7.6 bit    | 2 Channel           | 3-Wire, 4-Wire, Microwire, QSPI, SPI | 6.8 S/s                           | Differential/Pseudo-Differential/Single-Ended |

| 8 bit      | 2 Channel/3 Channel | 3-Wire, 5-Wire, SPI                  | 7.5 S/s                           | Differential/Single-Ended                     |

| 9 bit      | 2 Channel/4 Channel | 3-Wire, I2C, SPI                     | 10 S/s                            | Pseudo-Differential                           |

| 10 bit     | 3 Channel           | 3-Wire, JESD204, SPI                 | 12 S/s                            | Pseudo-Differential/Single-Ended              |

| 11 bit     | 3 Channel/5 Channel | 3-Wire, Parallel                     | 12.5 S/s                          | Single-Ended                                  |

| 12 bit     | 3 Channel/6 Channel | 3-Wire, Parallel, QSPI, SPI          | 13.7 S/s                          |                                               |

| 13 bit     | 4 Channel           | 3-Wire, Parallel, SPI                | 13.75 S/s                         |                                               |

| 14 bit     | 4 Channel/6 Channel | 3-Wire, QSPI, SPI                    | 15 S/s                            |                                               |

| 15 bit     | 4 Channel/7 Channel | 3-Wire, SPI                          | 16 S/s                            |                                               |

| 16 bit     | 4 Channel/8 Channel | 4-Wire                               | 16.6 S/s                          |                                               |

| 18 bit     | 5 Channel           | 4-Wire, 5-Wire, QSPI, SPI            | 16.7 S/s                          |                                               |

| 20 bit     | 6 Channel           | 5-Wire, Parallel                     | 19.79 S/s                         |                                               |

|            |                     | I2C, Parallel                        |                                   |                                               |

| Résolution | Nombre de canaux    | Type d'interface             | Taux d'échantillonage             | Type d'entrée                                 |

|------------|---------------------|------------------------------|-----------------------------------|-----------------------------------------------|

| 6 bit      | 1 Channel           | JESD204B                     | 3.75 S/s                          | Differential                                  |

| 7 bit      | 1 Channel/2 Channel | JESD204B, SPI                | 3.75 S/s, 15 S/s, 60 S/s, 240 S/s | Differential/Pseudo-Differential              |

| 7.6 bit    | 2 Channel           | Microwire, QSPI, SPI         | 6.8 S/s                           | Differential/Pseudo-Differential/Single-Ended |

| 8 bit      | 2 Channel/3 Channel | Parallel CMOS, Parallel LVDS | 7.5 S/s                           | Differential/Single-Ended                     |

| 9 bit      | 2 Channel/4 Channel | Parallel, Serial             | 10 S/s                            | Pseudo-Differential                           |

| 10 bit     | 3 Channel           | Parallel, SPI                | 12 S/s                            | Pseudo-Differential/Single-Ended              |

| 11 bit     | 3 Channel/5 Channel | QSPI, SPI                    | 12.5 S/s                          | Single-Ended                                  |

| 12 bit     | 3 Channel/6 Channel | Serial                       | 13.7 S/s                          |                                               |

| 13 bit     | 4 Channel           | Serial CMOS, Serial LVDS     | 13.75 S/s                         |                                               |

| 14 bit     | 4 Channel/6 Channel | Serial LVDS                  | 15 S/s                            |                                               |

| 15 bit     | 4 Channel/7 Channel | Serial, 2-Wire, I2C          | 16 S/s                            |                                               |

| 16 bit     | 4 Channel/8 Channel | Serial, 4-Wire, SPI          | 16.6 S/s                          |                                               |

| 18 bit     | 5 Channel           | SPI                          | 16.7 S/s                          |                                               |

| 20 bit     | 6 Channel           | UART                         | 19.79 S/s                         |                                               |

|            |                     | UART, 2-Wire                 |                                   |                                               |

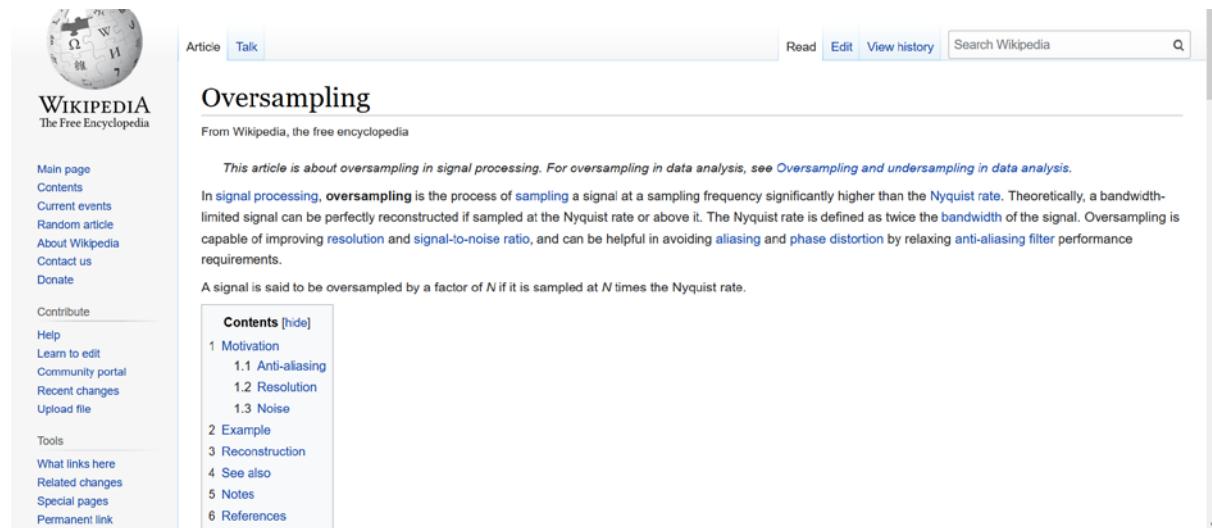

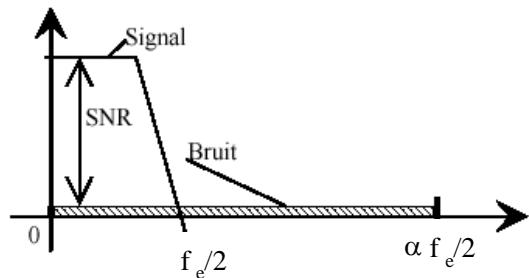

### c) Influence de la fréquence d'échantillonnage sur le bruit

The screenshot shows the Wikipedia page for "Oversampling". The page title is "Oversampling". The main content starts with a brief introduction: "This article is about oversampling in signal processing. For oversampling in data analysis, see [Oversampling and undersampling in data analysis](#). In signal processing, oversampling is the process of sampling a signal at a sampling frequency significantly higher than the Nyquist rate. Theoretically, a bandwidth-limited signal can be perfectly reconstructed if sampled at the Nyquist rate or above it. The Nyquist rate is defined as twice the bandwidth of the signal. Oversampling is capable of improving resolution and signal-to-noise ratio, and can be helpful in avoiding aliasing and phase distortion by relaxing anti-aliasing filter performance requirements." Below the text, there is a note: "A signal is said to be oversampled by a factor of  $N$  if it is sampled at  $N$  times the Nyquist rate." A sidebar on the left contains the Wikipedia logo and a navigation menu with links like Main page, Contents, Current events, Random article, About Wikipedia, Contact us, Donate, Contribute, Help, Learn to edit, Community portal, Recent changes, Upload file, Tools, What links here, Related changes, Special pages, and Permanent link.

#### 1.2 What is Undersampling?

If we use the sampling frequency less than twice the maximum frequency component in the signal, then it is called undersampling. Undersampling is also known as band pass sampling, harmonic sampling or super-Nyquist sampling. Nyquist-Shannon Sampling theorem, which is the modified version of the Nyquist sampling theorem, says that the sampling frequency needs to be twice the signal **bandwidth** and not twice the maximum frequency component, in order to be able to reconstruct the original signal perfectly from the sampled version. If  $B$  is the signal bandwidth, then  $F_s > 2B$  is required where  $F_s$  is sampling frequency. The signal bandwidth can be from DC to  $B$  or from  $f_1$  to  $f_2$  where  $B = f_2 - f_1$ .

The aliasing effect due to the undersampling technique can be used for our advantage. When a signal is sampled at a rate less than twice its maximum frequency, the aliased signal appears at  $F_s - F_{in}$ , where  $F_s$  is the sampling frequency and  $F_{in}$  is the input signal frequency. In the above case, if we sample the 70-MHz signal with 100 MSPS sampling rate, the aliased component will appear at 30 MHz ( $100 - 70$ ). As we know in advance that the signal is aliased, we can recover the actual frequency by using the  $F_s - F_{in}$  relationship. The undersampling technique allows the ADC to behave like a mixer or a down converter in the receive chain. For a band-limited signal of 70 MHz with a 20-MHz signal bandwidth, if the sampling rate ( $F_s$ ) is 100 MSPS, the aliased component will appear between 20 MHz to 40 MHz ( $30 \pm 10$  MHz).

<https://www.ti.com/lit/an/slaa594a/slaa594a.pdf>

Si on sur-échantillonne le même signal avec une fréquence  $\alpha f_e$ , avec  $\alpha > 1$ , on va diviser d'autant la densité spectrale du bruit qui va cette fois s'étaler entre  $-\alpha f_e/2$  et  $\alpha f_e/2$

Quel coefficient  $\alpha$  ?

Pourquoi un risque de débordement et comment y remédier ?

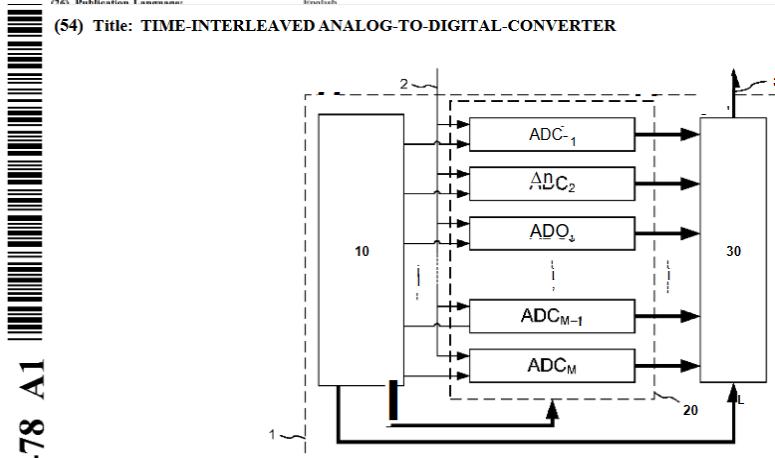

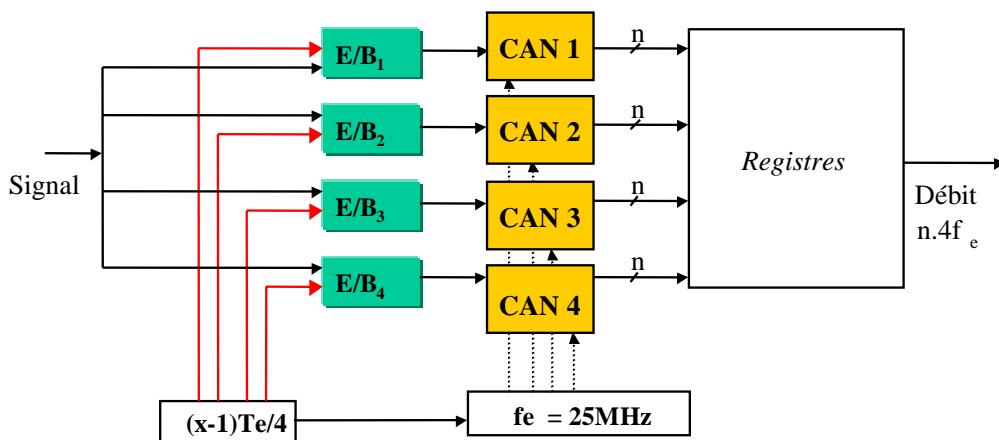

### d) Augmentation du débit d'information : l'entrelacement

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| (19) World Intellectual Property Organization<br>International Bureau |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (43) International Publication Date<br>23 August 2007 (23.08.2007)    | PCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (10) International Publication Number<br>WO 2007/093478 A1                        |

| (51) International Patent Classification:<br>H03M 1/12 (2006.01)      | (51) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TZ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW |                                                                                   |

| (21) International Application Number:<br>PCT/EP2007/050508           | (22) International Filing Date: 18 January 2007 (18.01.2007)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |

| (25) Filing Language:<br>English                                      | (26) Publication Language:<br>English                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |

(54) Title: TIME-INTERLEAVED ANALOG-TO-DIGITAL-CONVERTER

WO 2007/093478 A1

**(57) Abstract:** A method for operating a time-interleaved analog-to-digital converter for converting an analog input to a digital output using a time-interleaved analog-to-digital converter, wherein the time-interleaved analog-to-digital converter comprises an array of M sub ADCs ( $ADC_1, ADC_2, \dots, ADC_M$ ), where M is an even integer, and each row of the array comprises one of the M sub ADCs. The method comprises the step of, for every sampling instant n, where n is an integer in a sequence of integers, converting the analog input by means of the sub ADC in row  $k(n)$  of the array, wherein  $1 \leq k(n) \leq M$ . A value between 1 and M is assigned to  $k(n)$  for the first sample instant, and  $k(n+1)$  is selected such that a)  $k(n+1) > M/2$  if  $k(n) \leq M/2$ , otherwise  $k(n+1) \leq M/2$ ; b)  $M/2-1 \leq k(n+1)-k(n) \leq M/2+1$ ; and c)  $k(n+1) = k(m+1)$  if and only if  $n-m$  is an integer multiple of M. A time interleaved analog-to-digital converter operating in accordance with the method is also disclosed.

4AE SE « Chaines d'acquisition »

auteur : JY. FOURNIOLS

CAN et concepts

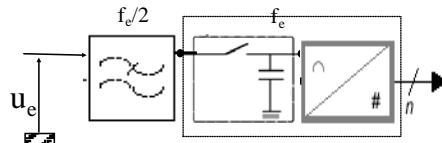

### e) Fonctionnement d'un CAN en régime dynamique

Intérêt des 3 trois phases dans le fonctionnement du CAN :

- la phase d'échantillonnage

- la phase de mémorisation ou blocage : démontrer pourquoi est-ce IMPERATIF à respecter ?

- la phase de codage

*f) Compression de dynamique et CODECS : exemple de la loi en A en téléphonie.*

Il existe également des techniques de codage qui tendent à diminuer le nombre de bits tout en garantissant un compromis sur la qualité de la conversion (les CODECS).

Pour illustrer le concept, le découpage de la pleine échelle jusqu'alors linéaire peut être non optimal le cas de signaux déterministes qui seraient statistiquement souvent bornés dans un intervalle I inclus dans la pleine échelle. Dès lors la précision peut être augmentée en diminuant le pas de conversion dans l'intervalle I tout en conservant le même nombre de bits de codage : c'est le principe d'un découpage logarithmique de la pleine échelle.

L'application au codage du son en téléphonie repose sur le principe de compression de dynamique plus connue en Europe sous l'appellation de loi de compression en A (« A-Law companding »). En effet, la perception des fréquences par les organes de Corti situés sur la membrane basilaire de la cochlée est parfaitement « logarithmique ».

La compression logarithmique de la loi en A, transforme un codage numérique linéaire d'une tension bipolaire sur 12 bits (11 bits + 1 bit de signe) en codage sur 8 bits (7 bits + 1 bit de signe).

Le principe de cette compression numérique de dynamique est le suivant :

L'intervalle des valeurs du code d'entrée y -codé sur 12 bits- s'étend de -2047 à 2047. Par symétrie sur la loi de codage, on considère l'intervalle de codes positifs [0,2047].

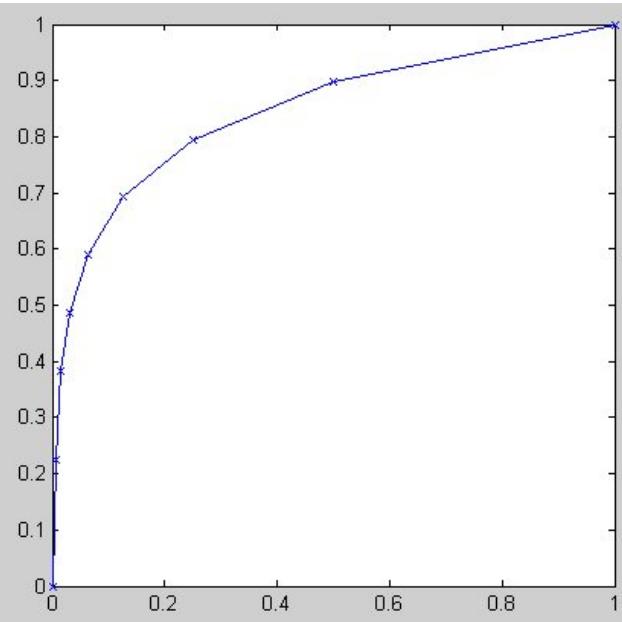

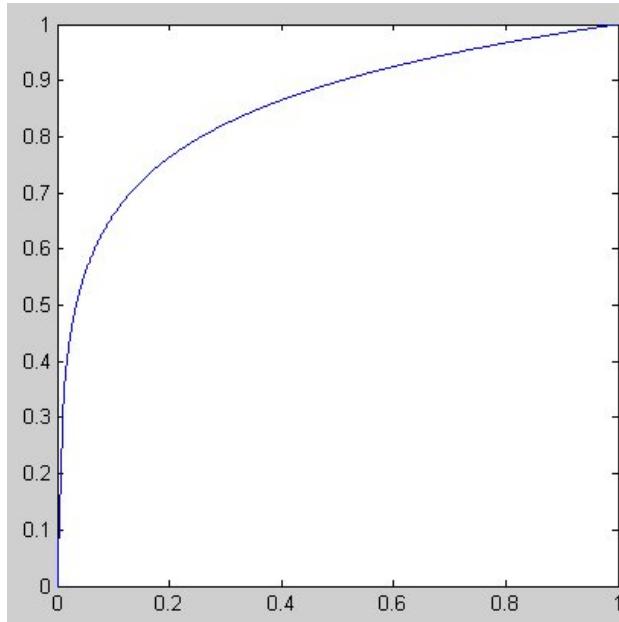

La loi de compression définie pour un code d'entrée normé à l'unité, soit la suite x définie par  $x=y/2047$ , est donnée par la relation :

$$F(x) = A \operatorname{sgn}(x) \frac{|x|}{1 + \log A} \quad 0 \leq |x| < \frac{1}{A}$$

avec la constante A égale à 87,6 en Europe, et sgn

$$F(x) = \operatorname{sgn}(x) \frac{1 + \log(A|x|)}{1 + \log A} \quad \frac{1}{A} \leq |x| \leq 1$$

fonction signe..

En traçant la fonction de compression logarithmique, on remarque que la loi en A peut être « linéarisée » par huit segments de droite (ou cordes) associés aux abscisses  $x_0=0$ ,  $x_1=1/128$ ,  $x_2=1/64$ ,  $x_3=1/32$ ,  $x_4=1/16$ ,  $x_5=1/8$ ,  $x_6=1/4$ ,  $x_7=1/2$ ,  $x_8=1$

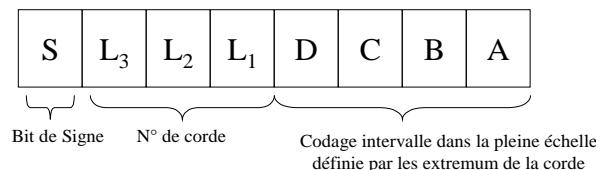

Le codage sur 8 bits s'effectue en deux étapes :

- identification de l'intervalle d'appartenance de l'échantillon  $x$ , et codage sur 3 bits du numéro du segment

- codage sur 4 bits (décomposition en 16 intervalles) de la fonction  $F(x)$  avec  $x$  variant entre les extrêmes définissant la corde.