# Technologie des circuit logiques : famille TTL et CMOS

## Différenciez les familles logiques

Pour appréhender la problématique de connecter des circuits logiques entre eux, il est nécessaire de répondre aux questions : un état logique "0" ou "1" est-il toujours le même pour différentes technologies ? Que se passe-t-il si on connecte une sortie logique à l'état 0 avec une autre sortie à l'état 1 ?

Dans les circuits numériques, deux technologies prédominent : la technologie **BIPOLAIRE** et la technologie **MOS**.

La technologie BIPOLAIRE est très souvent appelée TTL, mais elle découle de la mise en circuit de diodes et de résistances dans une évolution des technologies :

- **DL** : Diode Logic

- **RTL** : Resistor – Transistor Logic

- **DTL** : Diode – Transistor Logic

- **TTL** : Transistor – Transistor Logic

Afin d'analyser et de comprendre la genèse de la technologie TTL et les contraintes d'entrée et de sortance, décrivons cette évolution technologique dans les paragraphes suivants.

## Technologie DL (Diode LOGIC)

C'est la première famille logique créée à partir de l'utilisation d'éléments discrets de type diodes et résistances. Très vite abandonnée pour ses inconvénients de chute de tension dans les diodes et l'impossibilité d'obtenir le complément d'un signal logique (pas de porte inverseuse), cette technologie permet de se familiariser avec les notions de polarisation et d'états passants/bloqués.

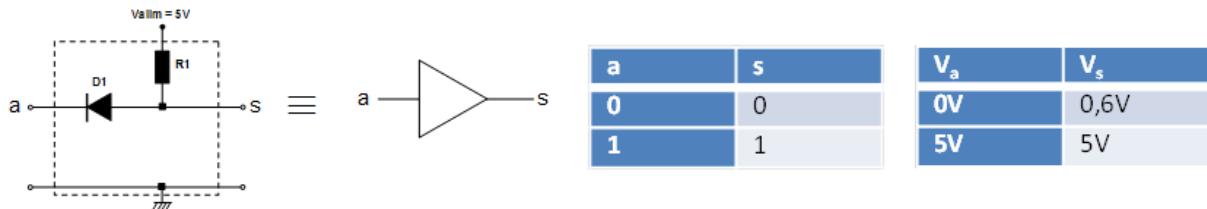

Cas de la fonction logique **OUI** :

- en connectant à la masse l'entrée a, la diode entre en conduction et impose à la sortie un potentiel  $V_s = V_{DVS} = V_D$  (tension de conduction de la diode souvent égale à 0.6V).

- de la même façon, un potentiel de 5V sur l'entrée (ou entrée en l'air), bloque la diode, d'où un potentiel  $V_s = R.i_{VS} = R.i$  soit  $V_s = 5V_{VS} = 5V$  pour une charge infinie connectée en sortie.

De ces deux cas, on en déduit que la sortie recopie l'entrée logique ; la fonction réalisée est la fonction **OUI**.

*Exemple avec la fonction OUI*

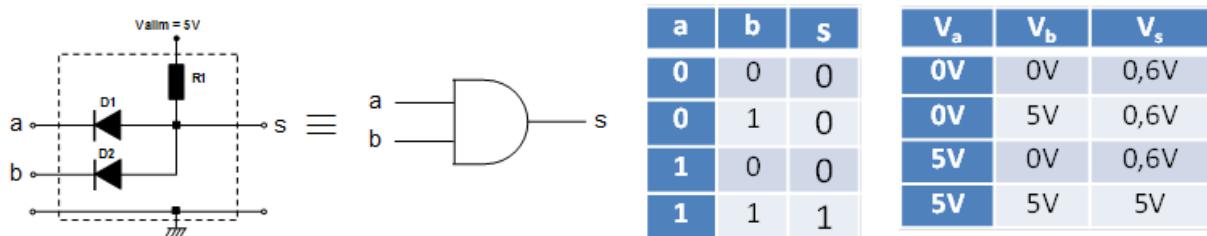

Avec la même approche, on démontre que le montage suivant réalise la fonction logique **ET**

*Exemple avec la fonction ET*

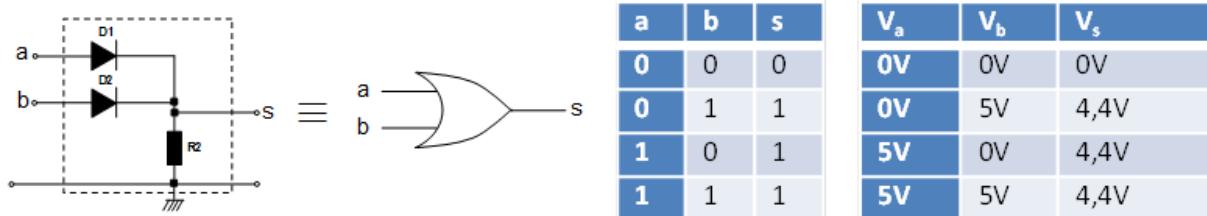

ou la fonction OU.

*Exemple avec la fonction OU*

## Technologie RTL (Resistor Transistor Logic)

---

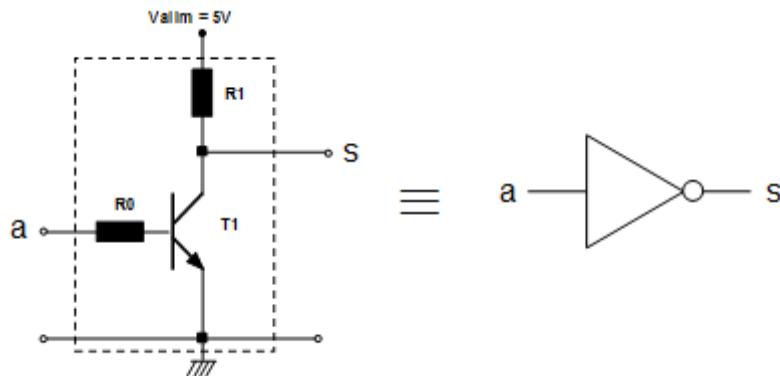

Les limites de la technologie DL ne permettent pas **d'assurer la fonction complément** (fonction NON). L'invention du transistor, le 23 décembre 1947, par trois ingénieurs américains des laboratoires Bell (John Bardeen, Walter Brattain et William Shockley), permet de pallier à ce défaut.

Analysons l'exemple du circuit ci-après, où le transistor fonctionne en régime bloqué/saturé et peut être vu comme un interrupteur à deux positions :

- $V_a=0V$   $V_a=0V$ , l'interrupteur est ouvert, le transistor est bloqué, la sortie  $V_s$  est au potentiel défini par  $V_s=V_{alim}-R_1i=V_{alim}=5V$   $V_s=V_{alim}-R_1i=V_{alim}=5V$  si la charge connectée est infinie, soit un niveau logique égal à "1",

- $V_a=5V$   $V_a=5V$ , l'interrupteur est fermé, le transistor est saturé,  $V_s=V_{CE}=0.2V$   $V_s=V_{CE}=0.2V$ , soit un niveau logique égal à "0".

*Schéma d'exemple : fonction NON*

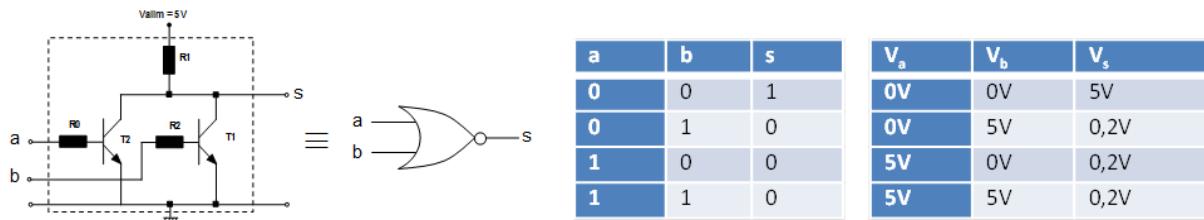

Avec la même approche, on démontre que le montage ci-après réalise la fonction logique NON OU.

*Schéma d'exemple : fonction NON OU*

## Technologie DTL (Diode Transistor Logic)

L'inconvénient de la technologie précédente était d'intégrer des résistances et d'avoir des temps de commutation s'affaiblissant avec le nombre croissant d'entrées. La combinaison des technologies DL et RTL va permettre de placer en entrée une diode, tout en conservant la capacité inverseuse du transistor pour créer des fonctions NON.

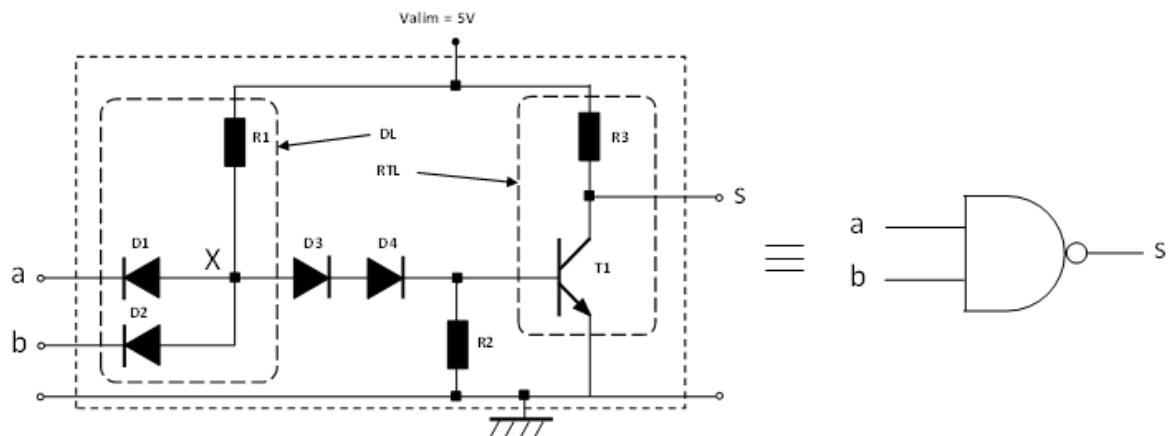

L'exemple suivant de fonction **NON ET** (ou NAND) associe en entrée une fonction **ET**, **en technologie DL**, puis la fonction **NON**, **en technologie RTL**.

*Exemple de fonction NON ET (NAND)*

Pourquoi avoir ajouté les diodes D<sub>3D3</sub> et D<sub>4D4</sub> ?

- Dans le cas où l'entrée a ou b est nulle, il faut garantir le blocage du transistor T<sub>1</sub> pour réaliser électriquement la fonction NAND que l'on souhaite créer.

- Sans les diodes D<sub>3D3</sub> et D<sub>4D4</sub>, le potentiel V<sub>xVX</sub> serait égal à V<sub>D</sub>=0.6V<sub>Vd</sub>=0.6V, impliquant la conduction du transistor T<sub>1</sub>. En plaçant D<sub>3D3</sub> et D<sub>4D4</sub>, on augmente V<sub>xVX</sub> à 3V<sub>D</sub>3V<sub>d</sub>, ce qui garantit le blocage de T<sub>1</sub>.

## Technologie TTL (Transistor Transistor Logic)

---

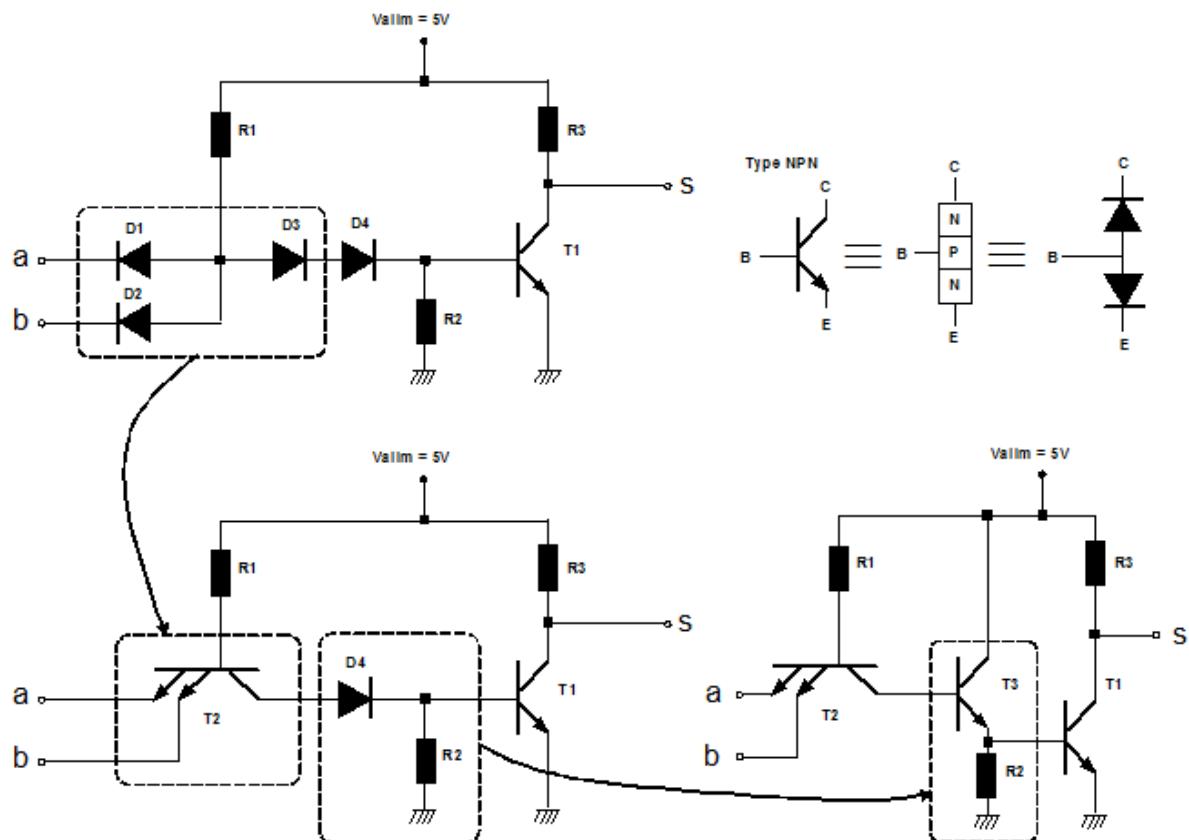

Les transistors étant réalisés sur silicium, la miniaturisation permet de considérer que deux jonctions PN à anodes communes (réalisées par 2 diodes) sont équivalentes à un transistor NPN, où l'appellation conserve cette notion de concaténation (NPN=NP+PN)(NPN=NP+PN).

La figure ci-après exploite cette spécificité d'intégration microélectronique et transforme la structure précédente en faisant apparaître des transistors à la place des diodes : on définit ainsi une intégration TOUT TRANSISTOR LOGIC, d'où la dénomination de cette technologie.

*intégration TOUT TRANSISTOR LOGIC*

### **Sortie totem pole ou collecteur ouvert ?**

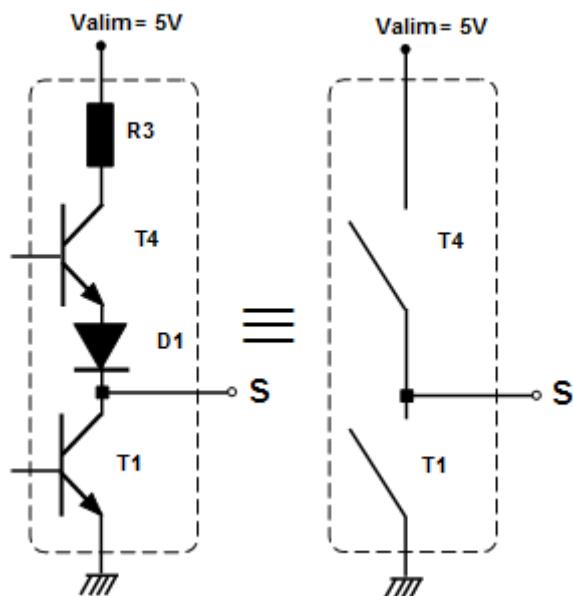

Se pose la question de l'étage de sortie de la porte logique, où l'on peut identifier deux types de sortie :

*Exemple*

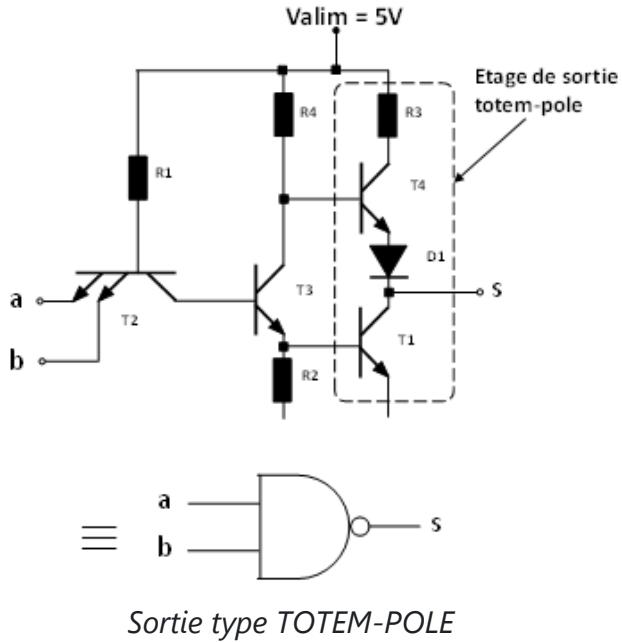

- **sortie type TOTEM-POLE :**

On améliore le temps de réponse de l'étage de sortie du montage précédent en rajoutant sur la partie supérieure à un transistor, dit montage **TOTEM-POLE**.

Notons aussi que le fait de supprimer la résistance permet de connecter une charge type capacitive sans introduire de constante de temps.

**La transformation de la fonction NON ET (NAND), de la technologie DTL en TTL TOTEM POLE, s'opère ainsi !**

Toutefois, il ne serait pas permis de connecter deux sorties TOTEM-POLE ensemble, au vu d'un risque de court-circuit, si les deux sorties étaient dans un état logique différent.

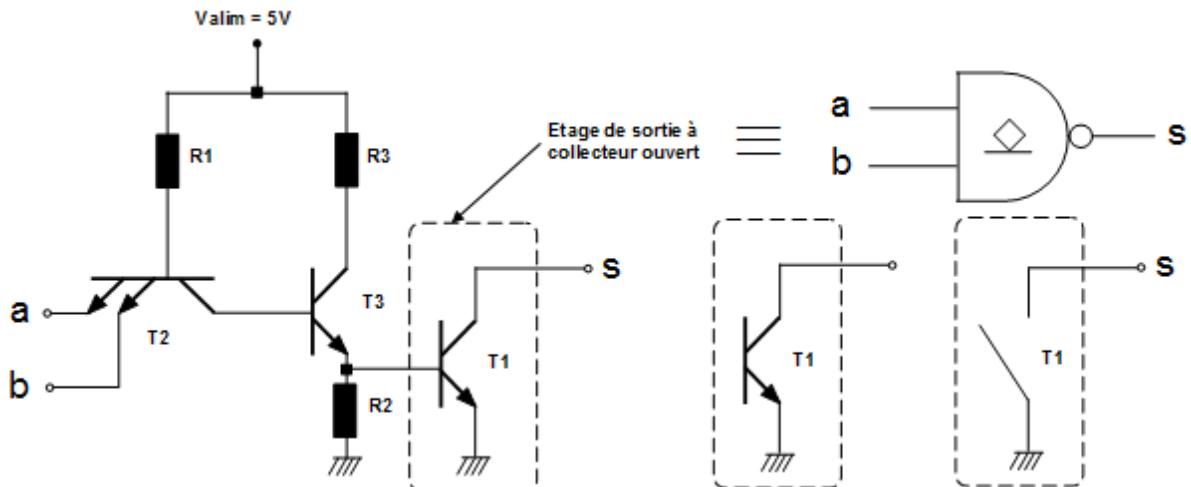

- **sortie collecteur ouvert :**

### *Sortie collecteur ouvert*

#### **Remarque :**

La technologie TTL (**T**ransistor **T**ransistor **L**ogic) constitue la technologie la plus ancienne. Les circuits TTL sont généralement alimentés en 0 et 5V :

- L'état haut est caractérisé par une tension d'environ 3.6V et l'état bas par une tension de 0.2V.

- Les tensions  $V_{IL}V_{IL}$  et  $V_{IH}V_{IH}$  sont égales à 1V et 2V.

- Le seuil de commutation en TTL est situé entre ces 2 tensions.

Cette dissymétrie, ainsi que la faiblesse des marges de bruit, rendent la technologie TTL sensible au bruit.

### **Technologie CMOS**

La technologie **CMOS** (**C**omplementary **M**etal **O**xyde **S**emiconductor) est la technologie la plus couramment utilisée au détriment de la technologie TTL.

"80 à 90 % des circuits numériques sont réalisés en technologie CMOS".

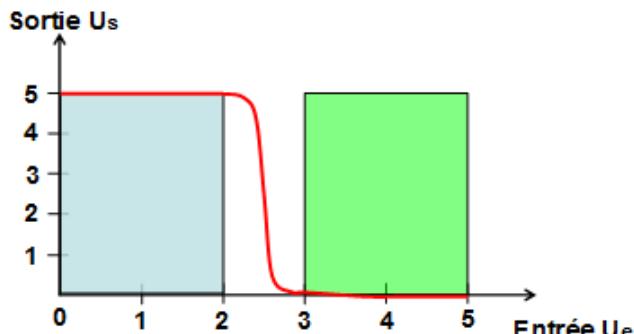

Les circuits **CMOS** ont des tensions d'alimentation allant généralement de 1V à 5V. La caractéristique de transfert  $U_s(U_e)U_s(U_e)$  d'un inverseur **CMOS** est très symétrique.

*Exemple d'un circuit CMOS*

Le niveau bas correspond à la tension d'alimentation basse (0V) et le niveau haut à la tension d'alimentation haute. La tension  $V_{IL}V_{IL}$  est égale à 30% de la tension d'alimentation (entre 1.5 et 2V) et  $V_{IH}V_{IH}$  à 70% de la tension d'alimentation (entre 3V et 3.5V). Le seuil de commutation de l'inverseur est situé à 2.5V. Les marges de bruit sont importantes, conférant à la technologie **CMOS** une bonne immunité au bruit.

Contrairement à la technologie **TTL**, la technologie **CMOS** n'absorbe ou ne fournit pas de courant en entrée, puisqu'elle présente une haute impédance.

Ainsi, la consommation d'un circuit **CMOS** est négligeable en régime statique et existe uniquement lors des phases dynamiques de transition (commutation).

## Comparaison CMOS/TTL

Ces deux familles technologiques présentent des différences en termes de niveau de tension à l'état haut et bas, d'immunité au bruit et de consommation de puissance.

| Famille                    | Sous famille | Symbol | Temps de propagation (ns) | Consommation statique (mW) |

|----------------------------|--------------|--------|---------------------------|----------------------------|

| TTL                        | Standard     | 74XX   | 10                        | 10                         |

| Basse consommation         | 74LXX        | 30     | 1                         |                            |

| Shottky basse consommation | 74LSXX       | 10     | 2                         |                            |

| Rapide                     | 74FXX        | 2      | 4                         |                            |

| CMOS                       | Standard     | 74CXX  | 50                        | 1                          |

| Rapide                     | 74HCXX       | 10     | 0.5                       |                            |

| Compatible TTL             | 74HCTXX      | 10     | 0.5                       |                            |

| Avancée                    | 74ACXX       | 3      | 0.5                       |                            |

### **Remarque :**

Les **entrées CMOS** ne consommant **pas de courant**, les **sortances** typiques des sorties **CMOS** sont **élevées** (de l'ordre de **50 Unités Logiques**).

Présentant une haute impédance, il est crucial de ne jamais laisser non connectées à un potentiel les entrées non utilisées d'un circuit. On énonce donc la règle de ne jamais laisser une entrée "en l'air".

## Vers le BiCMOS et les technologies radio...

En combinant les avantages des technologies TTL et CMOS, on obtient le BiCMOS (contraction de Bipolar-CMOS), qui permet la réalisation de circuits mixant des parties analogiques et numériques. D'autres technologies existent pour la réalisation de circuits Radio Fréquences dont les fréquences dépassent le GHz : citons par exemple les technologies AsGa, SiGe et SiC.

*Fan-in, fan-out, niveau logique, marge de bruit, TTL, CMOS font désormais partie du vocabulaire du concepteur en charge d'assurer l'intégrité électrique des signaux binaires.*